Hey there tech fam! If you’re gearin’ up for a VLSI or digital design interview, you’ve probs heard about Clock Domain Crossing (CDC). It’s one of them topics that can make or break your shot at landin’ a gig with top-tier companies. Interviewers love grillin’ candidates on CDC ‘cause it tests your grasp on some seriously tricky design challenges. So I’m here to break it down for ya—plain and simple—and walk you through the kinda clock domain crossing interview questions you’re gonna face. Let’s get you prepped to ace that chat!

I’ve been around the block with digital design and trust me CDC questions used to trip me up somethin’ fierce. But once I got the hang of it, I started seein’ patterns in what interviewers wanna hear. Stick with me, and we’ll cover the basics, dive into common and tough questions, and toss in some tips to make you sound like a pro. Ready? Let’s roll!

What the Heck is Clock Domain Crossing (CDC)?

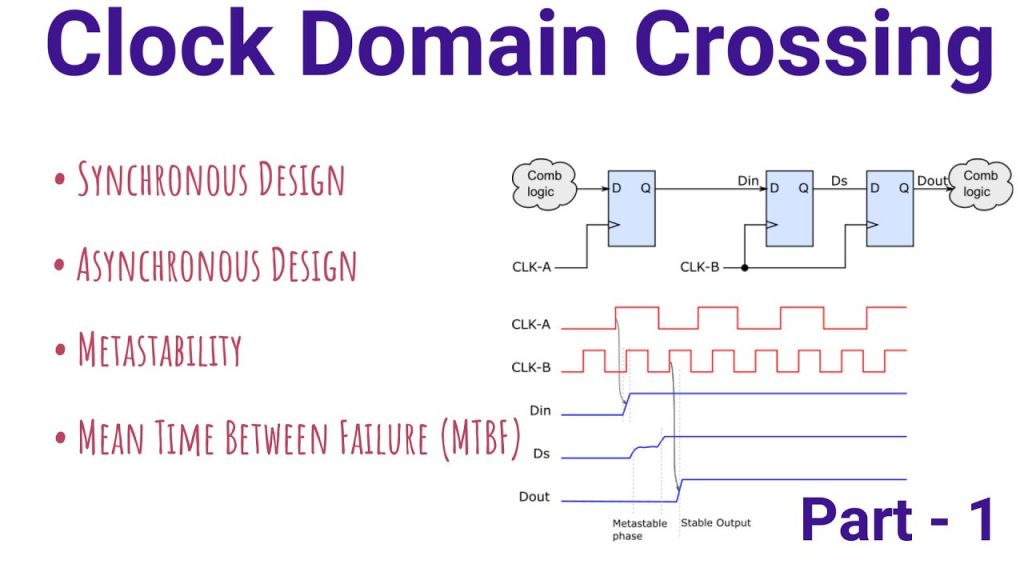

Before we jump into the interview Qs let’s make sure we’re on the same page about CDC. In digital design, especially in System-on-Chip (SoC) stuff you often got multiple clocks runnin’ at different speeds or outta sync with each other. Clock Domain Crossing is all about movin’ data from one clock domain (say, a fast 5ns clock) to another (maybe a slower 7ns clock) without screwin’ things up.

Why’s this a big deal? ‘Cause when clocks ain’t in sync, you can run into nasty issues like:

- Metastability: Where a flip-flop gets confused ‘cause data changes too close to a clock edge, makin’ the output unpredictable.

- Data Loss: Missin’ a signal ‘cause the receivin’ clock ain’t fast enough to catch it.

- Glitches: Weird timing errors messin’ with your logic.

In interviews, they wanna see if you get these risks and know how to handle ‘em with proper design tricks. So, let’s start with the kinda questions you might get asked, from the easy ones to the brain-busters.

Common Clock Domain Crossing Interview Questions (The Basics)

Interviewers often kick off with the fundamentals to see if you’ve got the groundwork down. Here’s some of the most common CDC questions I’ve seen pop up, along with how I’d tackle ‘em.

1. What is Clock Domain Crossing, and Why’s It Critical?

This is like the hello-world of CDC questions. They wanna know you get the concept.

- Answer Tip: Keep it short but sharp. “CDC is when data moves between two flip-flops runnin’ on different or async clocks. It’s critical ‘cause without proper handling, you risk metastability, data loss, or timing glitches. With today’s complex SoCs havin’ multiple clock domains for power or performance, messin’ this up can tank a design.”

2. What’s Metastability, and How Do Ya Deal With It?

Metastability is a buzzword in CDC, and they’ll def ask about it.

- Answer Tip: “It’s when a flip-flop’s input switches too close to the clock edge, violatin’ setup or hold times, so the output goes wonky or unstable. To fix it, I’d use a double-flop synchronizer for single-bit signals to give it time to settle. For bigger data, handshake protocols or async FIFOs work better. Oh, and Gray coding for counters helps too.”

3. What’s a 2-Flop Synchronizer, and When Do You Use It?

This one tests if you know the go-to solution for simple CDC.

- Answer Tip: “A 2-flop synchronizer is a setup with two flip-flops in series, both clocked by the destination domain. The first flop catches the async signal, and the second helps resolve any metastability. It’s great for single-bit control or status signals, like a reset or enable, ‘cause it’s low latency and small area.”

4. Why Can’t You Use 2-Flop Syncs for Multi-Bit Data?

A lil’ trickier, but still basic. They’re checkin’ if you know the limits.

- Answer Tip: “Each bit in a multi-bit bus can go metastable on its own, so usin’ separate 2-flop syncs per bit risks gettin’ inconsistent data. You lose coherency. Instead, I’d go for an async FIFO or a handshake mechanism to transfer the whole bus together safely.”

5. What’s an Asynchronous FIFO, and How’s It Help with CDC?

FIFOs come up a lot, so know this cold.

- Answer Tip: “An async FIFO is a buffer that lets you write data in one clock domain and read it in another. It’s got dual-port RAM, Gray-coded pointers to track read/write spots, and sync logic to handle full/empty flags. It’s perfect for multi-bit data transfer across domains without losin’ anything.”

These are your bread-and-butter questions. Nail ‘em, and you’ve shown you ain’t a newbie. But interviews for top VLSI gigs don’t stop here. They’re gonna throw some curveballs to see how deep you can go.

Tougher Clock Domain Crossing Interview Questions (Level Up!)

Once you’ve got the basics, interviewers might dig into more specific or scenario-based stuff. These questions test if you can apply theory to real design probs. I remember gettin’ stumped on a couple of these back in the day, so I’m givin’ ya the lowdown.

6. How Do You Handle a Pulse Transfer Between Clock Domains?

This one’s practical and sneaky. Pulses are short, so easy to miss.

- Answer Tip: “If I’m movin’ a single-cycle pulse from, say, a fast to a slow clock, there’s a risk the destination misses it. I’d stretch the pulse in the source domain to last a few cycles—maybe 3 or so—to make sure it’s caught. Then use a 2-flop sync to pass it over. In the destination, detect the risin’ edge. If frequencies vary a lot, a toggle synchronizer might be better—toggle a bit on pulse, sync it, and detect the change.”

7. What’s Gray Coding, and Why’s It Useful in CDC?

This pops up when talkin’ about pointers or counters.

- Answer Tip: “Gray coding is a way of countin’ where only one bit flips per step. It’s dope for CDC ‘cause it cuts the risk of errors when readin’ multi-bit values across domains. If multiple bits change at once in regular binary, a slow sync could read garbage. I’d use it for FIFO pointers or address transfers to keep things safe.”

8. Explain a Handshake-Based CDC Mechanism.

They might ask for a diagram or just the flow. Keep it clear.

- Answer Tip: “Handshake CDC uses a request-acknowledge dance. Source domain sends a ‘req’ signal with the data, syncs it to the destination. Dest domain latches the data, sends back an ‘ack’ signal, also synced. Source sees the ack, drops req, and dest drops ack. It’s reliable ‘cause it confirms every transfer, even if clocks are way outta whack. Great for occasional data or control stuff.”

9. How Do You Handle Reset Signals Across Clock Domains?

Resets are a common gotcha in CDC.

- Answer Tip: “Resets can be async, so direct crossin’ is risky—could cause random logic states. I’d sync the deassertion of the reset to the destination clock usin’ a 2-flop setup. Assertion can stay async, but deassertion gotta be clean to avoid glitches. Sometimes, a reset synchronizer circuit from the library does the trick.”

10. What CDC Issues Ain’t Caught by Static Timing Analysis (STA)?

This checks if you know STA’s blind spots.

- Answer Tip: “STA catches stuff like paths wrongly marked synchronous or bad constraints, but it misses CDC nasties like metastability ‘cause it’s analog, not digital. Also misses pulse stretchin’, data incoherency in buses, or handshake bugs. That’s why I’d use CDC-specific tools like SpyGlass or Questa to flag these issues.”

Advanced Scenarios and Brain-Teasers

For the big leagues, interviewers might throw out some real-world or edge-case questions. These ain’t just about book smarts—they wanna see how you think on your feet. Here’s a few I’ve come across or heard pals struggle with.

11. How Would You Transfer a Burst of Data Across Domains?

This one’s about throughput and design choice.

- Answer Tip: “For a burst, I’d pick an async FIFO over handshake ‘cause it handles high data rates better. Set the FIFO depth to match burst size, use Gray-coded pointers, and sync full/empty flags. If FIFO ain’t an option, a valid-ready handshake works, but it’s slower. Gotta watch for overflow with big bursts, though.”

12. What Happens if You Skip Syncin’ an Acknowledge in a Handshake?

A lil’ trap to see if you get protocol details.

- Answer Tip: “If ya don’t sync the ‘ack’ back to the source, it might think the transfer failed and resend data. That’s duplicate transfers or state machine chaos. Both req and ack gotta be synced to their domains, or you’re askin’ for corruption. I learned this the hard way debuggin’ a design once!”

13. Describe a CDC Bug You’ve Seen or Fixed.

They love personal stories—shows real experience.

- Answer Tip: “Once, I worked on a chip where an async reset wasn’t synced to local domains. After power-up, some flops initialized weird, causin’ random fails. We fixed it by addin’ reset synchronizers per domain and added assertions to catch glitches. Took forever to debug, but man, lesson learned—always sync resets!”

14. How Do You Design a CDC Interface for Fast-to-Slow Clocks?

Frequency diffs are a classic challenge.

- Answer Tip: “Fast-to-slow needs data held long enough for the slow clock to grab it. I’d use an async FIFO to buffer data, accountin’ for rate mismatch. For a pulse, stretch it or use a toggle sync. Gotta ensure no overflow on the FIFO and latch data stable till the slow domain reads it.”

15. Can Metastability Ever Be Fully Eliminated?

A philosophical one to test your depth.

- Answer Tip: “Nah, you can’t kill metastability completely—it’s just the nature of async crossings. But you can slash the odds with 2 or more flop syncs to give resolution time. Slower toggle rates help too. It’s all about reducin’ probability, not wipin’ it out. I’ve seen designs add extra flops just for that extra safety margin.”

Tips to Prep for CDC Interview Questions

Alright, now that we’ve covered a bunch of questions, let’s talk strategy. How do ya make sure you don’t freeze up when they hit ya with a CDC curveball? Here’s my no-BS advice based on scrapin’ through interviews myself.

- Brush Up on Basics First: If you can’t explain metastability or a 2-flop sync without stutterin’, you’re toast. Start with the core stuff—CDC definition, risks, simple fixes. I used to write these out on sticky notes and quiz myself.

- Draw It Out: In interviews, they might ask for diagrams (like handshake timing). Practice sketchin’ sync circuits or FIFO setups on paper. I flubbed a timing diagram once ‘cause I didn’t prep—don’t be me.

- Know Your Tools: Mention CDC tools like Synopsys SpyGlass or Mentor Questa. It shows you’ve got industry know-how. I dropped a tool name in an interview once, and the guy’s eyes lit up like I’d said somethin’ magical.

- Think Scenarios, Not Just Theory: They might give ya a setup—two clocks, diff frequencies, transfer a pulse. Walk through it step-by-step: risks, solution, why. Practice with made-up probs to build that muscle.

- Admit When You’re Stumped (Kinda): If a question’s outta left field, don’t BS. Say, “Hmm, I ain’t tackled that exact case, but here’s how I’d approach it…” and reason aloud. I did this once, and they liked the honesty.

Common Mistakes to Dodge

I’ve seen folks—and heck, I’ve done it myself—trip over some dumb stuff in CDC questions. Watch out for these traps:

- Forgettin’ Multi-Bit Issues: Sayin’ 2-flop sync works for buses. Nope, it don’t. Always mention FIFO or handshake for data coherency.

- Ignorin’ Frequency Gaps: If clocks are way different speeds, your solution gotta account for it. Don’t assume equal rates.

- Skippin’ Sync for Resets or Acks: Every control signal crossin’ domains needs sync. Missin’ one in your answer looks sloppy.

- Overcomplicatin’: Don’t suggest a crazy FIFO for a single-bit flag. Match the solution to the problem. I over-engineered an answer once and got called out—ouch.

Why CDC Matters So Much in Interviews

Lemme tell ya why companies are obsessed with CDC. In modern chips, you’ve got tons of clock domains—some for power savin’, some for performance, some just ‘cause IPs got their own clocks. If data ain’t crossed right, your whole design could glitch out, costin’ millions in respins. So, they need engineers who get this stuff inside out. Show ‘em you can spot CDC risks and slap on the right fix, and you’re golden.

I remember chattin’ with a hiring manager after an interview, and he straight-up said, “We grill on CDC ‘cause one bad crossing can kill a project.” That stuck with me. It ain’t just a test—it’s about trustin’ you with their silicon.

Wrappin’ It Up: Be the CDC Champ

So, there ya have it—a deep dive into clock domain crossing interview questions to get you ready to slay that VLSI interview. We covered what CDC is, why it’s a pain, the easy questions to warm up with, the tough ones to prove your chops, and even some pro tips to stand out. I’ve thrown in my own stumbles and wins to keep it real—hope it helps ya feel less alone in this grind.

Bottom line? CDC ain’t just tech jargon—it’s a core skill for digital design. Master these concepts, practice explainin’ ‘em clear and confident, and you’ll walk into that interview room like you own it. Got a fave CDC question or a horror story from an interview? Drop it in the comments—I’d love to hear! And hey, good luck out there, fam. You got this!